Übungen Digitaltechnik mit Lösungen Unterrichtsblätter zum Download

Üblicherweise wurde die Digitaltechnik mit TTL oder CMOS ICs umgesetzt mit der 74LSxxx oder 74HCTxxx Serie umgesetzt. In er Praxis macht das jedoch niemand mehr. Die Lösung von digitalen Schaltungen wird mit programmierbaren Logikbausteinen realisiert.

Die Inhalte der Digitaltechnik wurden auf der Hardware einer programmierbaren Logik umgesetzt.

Als Programmiersprache wurde ABEL verwendet. Inzwischen ist VHDL üblich, was jedoch deutlich komplexere Programmierkenntnisse benötigt.

Dazu wurde eine CD mit folgenden Inhalten zusammengestellt:

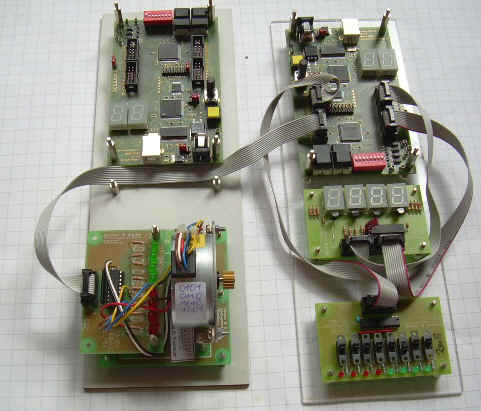

Dazu haben wir zwei Platinen entwickelt in enger Zusammenarbeit mit Otto Bubbers ein Kollege aus Karlsruhe/Sindelfingen:

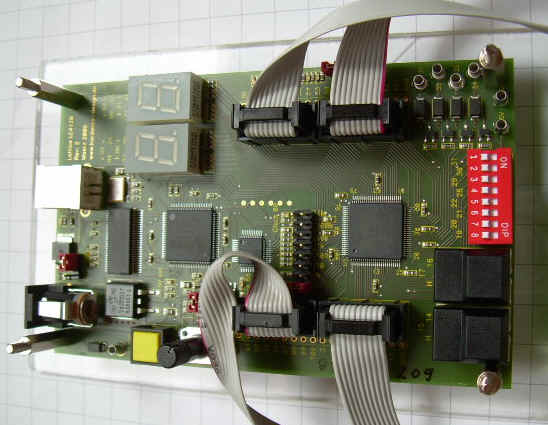

- Alte Platine mit LPT parallele Schnittstelle zum programmieren der Hardware

Baustein MACH 4A5 64/32 mit 4 Programmierfeldern, 64 D-FFs und 32 Ein- /Ausgänge

2. Neue Platine mit USB Programmierschnittstelle:

Der neue Baustein ist der ispMACHLC4128V mit deutlich mehr FlipFlop-Funktionen und genügend Ein-/Ausgängen.

mit Anwendungsbeispiele:

Hier eine Aufgabenstellung mit der gemultiplexten 7Segment Anzeige:

-Zuerst werden 2 Anzeigen gemultiplext. Sichtbar werden jeweils eine Dualzahl mit 4bit. Diese 4bit werden als Zahl auf der Anzeige dargestellt. Der Rechteckgenerator auf der Platine schaltet die Anzeigen ein und aus. Bei langsamer Taktrate sieht man, wie die Anzeigen nacheinander eingeschaltet werden. Bei schneller Taktrate sieht man beide Anzeigen leuchten, eben der Multiplexeffekt. Diese Aufgabe ist schon anspruchsvoller, zeigt jedoch, wie einfach man eine komplexe digitale Schaltung realisieren kann. Natürlich ist die Entwicklungsumgebung von Lattice notwendig. Wer in die programmierbare Logik einsteigen will hat schon einige Hürden zu nehmen…….

Ein paar einfachere Beispiele:

Eine einstellige 7Seg-Anzeige mit einem synchronen Zähler 0 bis 9 und einem dual auf 7Seg-Decoder. Zuerst der Entwurf des Zähler klassisch mit Wahrheitstabelle und KV-Tafel. Dann die Lösung in ABEL. ABEL macht die Verknüpfungenfür die D-FFs aus der Wahrheitstabelle (Truth Table) automatisch.

Ein Beispiel, wie man die Funktionsgleichungen für die Beschaltung der D-FFs aus einer Wahrheitstabelle selbst ermittelt. Dargestellt für einen Zähler 0 bis 5 und einen Zähler 0 bis 9. Zusammengeschaltet gibt das einen Sekundenzähler.

Hier das Arbeitsblatt für den Zählerentwurf: